Del 23-01-2013 al 25-01-2013

Síntesis de alto nivel para FPGAs de Xilinx con Vivado-HLS (AutoESL)

Síntesis de alto nivel para FPGAs de Xilinx con Vivado-HLS (AutoESL)

El diseño digital ha evolucionado de los lenguajes de descripción de hardware (HDL – Hardware Description Languages) a los lenguajes de alto nivel (HLL – High Level Languages). En este curso se estudian las estrategias para el uso de las herramienta de síntesis para obtener diseños digitales eficientes a partir de descripciones en C/C++. Se aprenden los conceptos de optimización de área y velocidad en el contexto de la síntesis de alto nivel.

Los descriptores preliminares son:

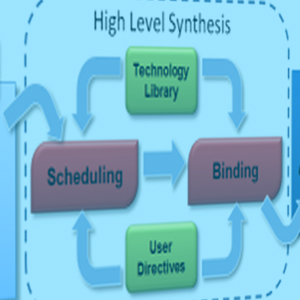

Introducción a la Síntesis de alto nivel (HLS – High Level Synthesis). Conceptos de planificación y enlace (scheduling and Binding)

Comprender el flujo de diseño HLS en AutoESL. Introducción a la herramienta.

Optimizaciones de performance. Terminología: Latencia, productividad, intervalo de inicialización. Desenrollamiento, mezcla y aplanamiento de bucles, segmentación (pipeline) a nivel funciones y bloques. Acceso concurrente a arreglos

Optimizaciones de área. Control de recursos utilizados. Reúso de componentes. Mantenimiento de jerarquías (inlining). Mapeo y reordenamiento del almacenamiento (array mapping). Precision en los operadores.

Directivas para el control de velocidad y el área. Ejemplos de utilización. Nociones de TCL para el manejo de la herramienta.

Testbenches en C/C++. Flujo de validación. Simulación de sistemas desde system-C y usando HDLs con modelsim.

Codificación en C/C++ para diseño de Hardware. Tipos de datos de ancho no estándar, construcciones no soportadas: punteros, mallocs, etc. Uso de Volatiles. Uso de streaming.

Manejo de Interfaces de entrada Salida. Modelos de computación e intercomunicación en HLL. Creación de cores-IP tanto para EDK, interfaces AXI y conexión con VIVADO.

Prerrequisitos:

Conocimientos de lenguajes de descripción de HW (VHDL ó Verilog). Nociones de uso de FPGAs.

Fechas:

Miércoles 23, jueves 24 y viernes 25 de enero de 2013 (3 días – 24 hs de curso).

Matrícula:

Curso completo tres días: 750 €

El precio incluye el material del curso, comidas y cafés.

El curso posee una bonificación del 10% por asistencia a otros cursos previos y del 20% para más de dos asistentes de la misma empresa/institución.

Lugar:

Escuela Politécnica Superior

Universidad Autónoma de Madrid (UAM)

Francisco Tomás y Valiente, 11

28049 MADRID

Como llegar a la EPS-UAM (aquí).

Fundación Tripartida

Recuerde que su empresa puede beneficiarse de las subvenciones de la fundación tripartita.

Pre-inscripción:

[Inscripción cerrada]

Fotos del evento

A continuación mostramos algunas fotos del evento:

Galería de imágenes

Profesores a cargo:

-

Gustavo Sutter

Doctor en informática y telecomunicaciones por la Universidad Autónoma de Madrid, Ingeniero en Sistemas en la Univ. Nacional del Centro de la Prov. de Buenos Aires en Argentina. Cuenta con más de 15 años de experiencia en diseño de sistemas...Leer Más -

Sergio Cuenca Asensi

Sergio Cuenca Asensi es profesor Titular en el departamento de Tecnología Informática y Computación de la Universidad de Alicante. Doctor en Informática desde el año 2002, sus principales líneas de interés son la Computación Reconfigurable, el Co-diseño Hw/Sw y el...Leer Más -

Raúl Mateos Gil

Raúl Mateos Gil es doctor por la Universidad de Alcalá e Ingeniero de Telecomunicación por la Universidad Politécnica de Madrid. Actualmente es profesor titular del Departamento de Electrónica de la Universidad de Alcalá. Sus áreas de investigación se centran en...Leer Más -

Sergio Lopez-Buedo

El Dr. Sergio López Buedo, es profesor contratado doctor en el área de Arquitectura y Tecnología de Computadores de la UAM y socio fundador de NAUDIT, una empresa de base tecnológica spin-off de dicha universidad. Tiene más de 15 años...Leer Más