03-10-2019

Free Workshop: Hand-On introduction to High Level Synthesis using Xilinx Vivado-HLS

Taller gratuito: Introducción práctica a la síntesis de alto nivel usando Xilinx Vivado-HLS

Electratraining con la colaboración de Silica-Avnet como distribuidor de Xilinx organizan este taller aplicado.

Presentation (in Spanish below):

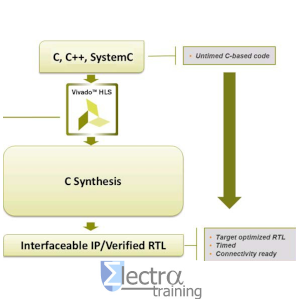

This Hands-on introduction shows how high-level synthesis using Vivado-HLS can be used to take advantage of the scalable pipeline parallelism present in FPGAs. Attendees will learn how to target FPGA resources from high-level C/C++ or OpenCL code, guiding the mapping from imperative code to hardware, enabling them to develop massively parallel designs achieving significant performance benefits in minutes.

By bridging the gap between software and hardware design, our tutorial aims to enable developers from a larger set of different backgrounds to start harnessing into the potentials of FPGAs. In addition we will show how easy is to generate interfaces and IP-cores to be integrated into the Xilinx FPGAs design Flow.

The seminar will be in Spanish. The seminar is free, but requires registration. The organization will provide computers with the installation of the necessary tools to carry out the workshop. We will confirm places one week in advance.

Presentación:

Esta introducción práctica muestra cómo se puede utilizar la síntesis de alto nivel con Vivado-HLS para aprovechar el paralelismo y la posibilidad de segmentación (pipeline) presente en los FPGA. Los asistentes aprenderán cómo instanciar recursos de la FPGA a partir de código de alto nivel en C / C ++ u OpenCL, guiando la asignación del código imperativo al hardware. Esto permite desarrollar diseños masivamente paralelos logrando importantes beneficios de rendimiento en pocos minutos de desarrollo.

Al cerrar la brecha entre el diseño de software y hardware, nuestro tutorial tiene como objetivo permitir que desarrolladores de diferentes areas comiencen a aprovechar el tremendo potencial de los FPGA. Además, mostraremos cuan fácil que es generar interfaces y cores-IP que se integren en el flujo de diseño de FPGA de Xilinx.

El workshop será en español y gratuito, pero requiere registro. La organización proveera ordenadores con la instalación de las herramientas necesarias para realizar el taller. Confirmaremos las plazas con una semana de anticipación.

Content / Contenido:

- Introduction to High-Level Synthesis (HLS). How is HW extracted from C/C++ code, scheduling and binding, C Functions and RTL hierarchy, operators, loops, arrays in C, Validation flow.

- Using Vivado HLS. Vivado HLS GUI mode, projects, synthesis, IP-XACT flow, design analysis, TCL in Vivado

- Lab: Creating Project and Understanding Reports

- Improving Performance and Area. Use of directives. Improve latency manipulating loops: unrolling, flattening, and merging. Improving thoughput: Dataflow and Pipelining. Performance bottlenecks. Array partitioning and reshaping. Improving Area and Resources Utilization.

- Lab: Optimizing Performance through Pipelining and reducing Area and Resources Utilization

- Interfacing HLS modules. Block- and Ports- Level Protocols. How interface with the outside world. Block level protocols, IP adapters (AXI4, AXI4LiteS and AXI4Stream), port level handshakings.

- Integrating HLS block in IP-design Flow, in Embedded Design Flow and in acceleration context (notions of SDAcell).

- Lab: Reviewing previous concept and integrating in an embedded example.

Preliminary Agenda / Agenda Preliminar:

- 9.15 Registration

- 9.30 Welcome and presentation

- 9.45 First Part: Intro-HLS

- 11:15 Short Break

- 11:30 Second Part: Improving Performance and Area.

- 13:00 Lunch Time

- 14.30 Third Part: Integrating HLS blocks

- 16.15 Recap, discussion and Questions.

- 16.30 End of event

Date / Fecha:

Thursday, October 3, 2019 from 9.30 a.m. to 4:30 p.m. / Jueves 3 de octubre de 2019 de 9.30 a 16:30.

Place / Lugar realización:

Escuela Politécnica Superior

Universidad Autónoma de Madrid (UAM)

Francisco Tomás y Valiente, 11

28049 MADRID

Puede ver como llegar (Aquí).

Registration / Registro:

[Evento realizado]

Galería de imágenes

Profesores a cargo:

-

Sergio Lopez-Buedo

El Dr. Sergio López Buedo, es profesor contratado doctor en el área de Arquitectura y Tecnología de Computadores de la UAM y socio fundador de NAUDIT, una empresa de base tecnológica spin-off de dicha universidad. Tiene más de 15 años...Leer Más -

Gustavo Sutter

Doctor en informática y telecomunicaciones por la Universidad Autónoma de Madrid, Ingeniero en Sistemas en la Univ. Nacional del Centro de la Prov. de Buenos Aires en Argentina. Cuenta con más de 15 años de experiencia en diseño de sistemas...Leer Más