10-11-2022

Seminario: Versal ACAP, impulsando el rendimiento y la productividad

Seminar: Versal ACAPs, boosting performance and productivity

Seminario: Versal ACAP, impulsando el rendimiento y la productividad

Presentación (In English below):

El rápido crecimiento de las tecnologías que impulsan aplicaciones de uso intensivo de datos, como 5G, IA y aprendizaje automático, ha puesto a prueba las capacidades de las CPU, GPU, FPGA y SoC tradicionales. Con la ralentización de la Ley de Moore mermando significativamente las ventajas de pasar a nodos de proceso más pequeños, la innovación arquitectónica es imprescindible para cualquier dispositivo que pretenda resolver los desafíos que plantean estas y otras aplicaciones exigentes.

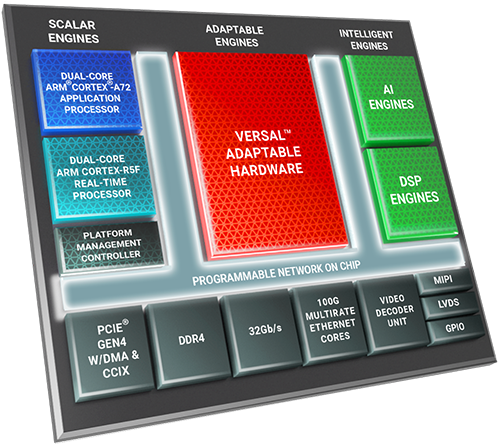

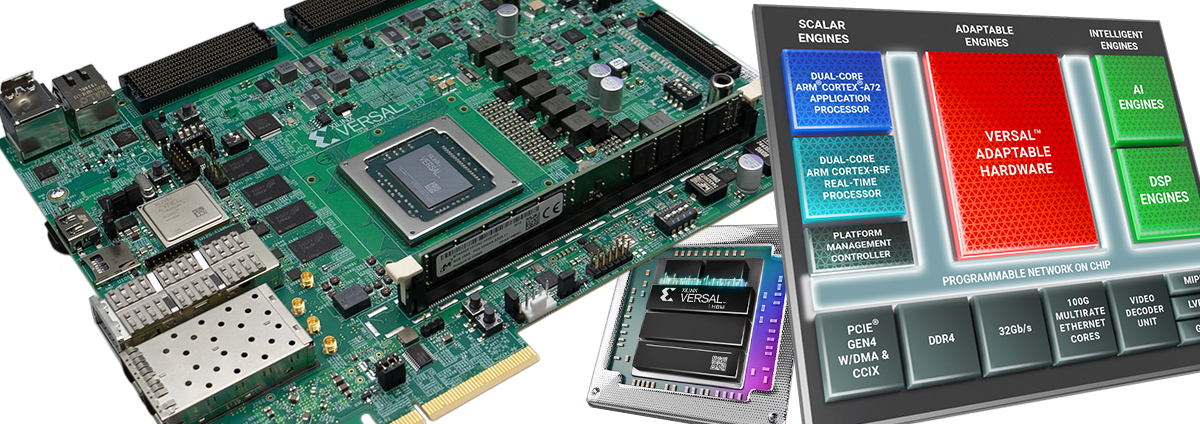

Las plataformas de aceleración de computación adaptable (ACAP – adaptive compute acceleration platforms) presentes en Versal® representan una evolución significativa con respecto a los FPGA y SoC tradicionales, y complementan las fortalezas de la lógica programable tradicional con potentes motores de cómputo heterogéneos y una nueva infraestructura de silicio programable por software.

En este seminario web, cubriremos lo siguiente:

- Visión general de la arquitectura Versal y las diferentes familias

- Cómo la arquitectura Versal ofrece ganancias de rendimiento a nivel de sistema

- Una demostración de la red programable en chip (NoC – Network on Chip), una de las características clave que acelera la productividad para los diseñadores de sistemas.

- Flujos de diseño de Vitis para dispositivos Versal.

- Actualizaciones de productos Versal ACAP: Versal AI edge, HBM, Prime y AI core.

La aparición de esta nueva generación de plataformas de aceleración adaptable (ACAP – Adaptive Compute Acceleration Platforms) abre nuevas posibilidades para los desarrolladores de software y hardware.

Estas plataformas integran una arquitectura de cómputo heterogénea con CPU, GPU y FPGA, lo que permite el desarrollo de motores escalares, adaptables e inteligentes, estrechamente acoplados con jerarquías de memoria personalizadas y una red en chip (NoC – Network on Chip). Esté a la vanguardia de las tecnologías FPGA y aprenda a utilizar la plataforma FPGA de próxima generación de Xilinx: ¡Versal® ACAP!

Este seminario patrocinado por Xilinx y ElectraTraining en su rol de training autorizado (ATP – Xilinx Authorized Training) permite comenzar a trabajar con la nueva plataforma Versal ACAP, explorar las características exclusivas de Versal, como los AI Engine y Network-on-Chip (NoC). Además, obtendrá más información sobre los flujos de diseño en la herramienta de software unificado Vitis.

Introduction

The rapid rise of technologies driving data-intensive applications such as 5G, AI, and machine learning has strained the capabilities of CPUs, GPUs, FPGAs, and SoCs. With the end of Moore’s Law significantly limiting the advantages of moving to smaller process nodes, architectural innovation is a must for any devices intending to solve the challenges posed by these and other demanding applications.

Versal® adaptive compute acceleration platforms (ACAPs) represent a significant evolution over traditional FPGAs and SoCs, supplementing the strengths of traditional programmable logic with powerful heterogeneous compute engines and a new software-programmable silicon infrastructure.

These platforms integrate a heterogeneous compute architecture with CPUs, GPUs and FPGAs, enabling the development of scalar, adaptable and intelligent engines, tightly coupled with custom memory hierarchies and a Network-on-Chip.

In this webinar, we’ll cover the following:

- An overview of the Versal architecture and the Versal series

- How the Versal architecture delivers performance gains at the system-level

- A demonstration of the programmable network on chip (NoC), one of the key features accelerating productivity for system designers

- Vitis design flows for Versal devices.

- Versal ACAP product updates: Versal AI edge, HBM, Prime and AI core.

The emergence of a new generation of Adaptive Compute Acceleration Platforms opens up new possibilities for both software and hardware developers.

This webinar sponsored by AMD-Xilinx a allows you to start working with the new Versal ACAP platform, explore the exclusive features of Versal, such as the AI Engine and Network-on-Chip (NoC). You will also learn more about design flows in the Vitis Unified Software Tool.

*The seminar will be in Spanish

Descriptores / Contents:

Información preliminar, más detalles en breve:

- Introduction. Talks about the need for Versal devices and gives an overview of the different Versal families.

- Architecture Overview.

- Design Flows and demos

- Q&A

Fecha:

- Jueves 10 de noviembre de 2022 de 14:00 a 18:00h. (horario coordinado Europeo de verano)

Date:

- Thursday, november 10th 2022 14:00 – 18:00 CEST.

Lugar de realización:

Live on Line

Pre-registro:

[Evento Finalizado]

Profesores a cargo:

-

Sergio Lopez-Buedo

El Dr. Sergio López Buedo, es profesor contratado doctor en el área de Arquitectura y Tecnología de Computadores de la UAM y socio fundador de NAUDIT, una empresa de base tecnológica spin-off de dicha universidad. Tiene más de 15 años...Leer Más -

Gustavo Sutter

Doctor en informática y telecomunicaciones por la Universidad Autónoma de Madrid, Ingeniero en Sistemas en la Univ. Nacional del Centro de la Prov. de Buenos Aires en Argentina. Cuenta con más de 15 años de experiencia en diseño de sistemas...Leer Más -

Raúl Mateos Gil

Raúl Mateos Gil es doctor por la Universidad de Alcalá e Ingeniero de Telecomunicación por la Universidad Politécnica de Madrid. Actualmente es profesor titular del Departamento de Electrónica de la Universidad de Alcalá. Sus áreas de investigación se centran en...Leer Más