18-05-2023

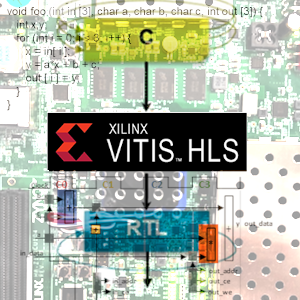

Seminario: Síntesis de alto nivel (HLS) en el ecosistema AMD-Xilinx Vitis

— Grabaciones parciales del evento al final de la página

Workshop: Increase your productivity using High Level Synthesis in the AMD-Xilinx Vitis ecosystem

Entiende con nosotros porque DEBES conocer los beneficios del uso de la síntesis de alto nivel (HLS) y comienza a utilizarla.

La síntesis de alto nivel es el proceso que, partiendo de una descripción de diseño abstracto (solo funcional), traduce y optimiza en una descripción a lenguaje de transferencia de registros (RTL) que sea sintetizable lógicamente. Las herramientas de síntesis de alto nivel realizan numerosas optimizaciones, como la programación y el uso compartido de recursos para mejorar el rendimiento, área y consumo del diseño.

Presentación (In English below):

Este seminario muestra las ventajas en tiempo de desarrollo y productividad de las estrategias de síntesis de alto nivel (HLS) y su integración en la herramienta Vitis. Se describe tanto para el desarrollo de IP-Cores para sistemas embebidos desde C/C++, como la estrategia de aceleración para sistemas completos que parten de una descripción de alto nivel.

AMD-Xilinx está lanzando plataformas de desarrollo nuevas y cada vez más potentes (como Versal ACAP), pero también herramientas para aumentar la productividad de los diseñadores. Vitis Unified Software Platform ofrece muchas opciones, bibliotecas y flujos de diseño para cubrir escenarios diferentes y complejos. El uso eficiente de la síntesis de alto nivel usando Vitis-HLS es esencial para explotar todo el potencial del ecosistema Vitis.

Introduction

This seminar shows the advantages in development time and productivity of high-level synthesis strategies (HLS) and their integration in the Vitis tool. It is described both for the development of IP-Cores for embedded systems from C/C++, as well as the acceleration strategy for complete systems that start from a high-level description.

AMD-Xilinx is launching new and increasingly powerful development platforms (such as Versal ACAP), but also tools to increase designer productivity. Vitis Unified Software Platform provides many options, libraries and design flows to cover different and complex scenarios. The efficient use of high-level synthesis using Vitis-HLS is essential to exploit the full potential of Vitis ecosystem.

*The seminar will be in Spanish

Descriptores / Contents:

- 14:00 – Intro seminar

- AMD-Xilinx Platforms and Tools

- Introduction to High-Level Synthesis

- Vitis HLS Tool Flow

- Demo 1 – Intro HLS

- 15.30 approx. – 1st BREAK

- Kahoot 1

- Design Exploration with Directives

- Introduction to IO Interfaces

- Demo 2 – Directives & interfaces

- 16.55 approx. – 2nd BREAK

- Kahoot 2

- Introduction to the Vitis Unified Software Platform

- What’s New in Vitis HLS 2022.2

- 17:45 Q&A

- 18:00 End Session

Fecha:

- Jueves 18 de mayo de 2023 de 14:00 a 18:00h. (horario coordinado Europeo de verano)

Date:

- Thursday, may 18th 2023 14:00 – 18:00 CEST.

Lugar de realización:

Live on Line

Pre-registro:

[evento finalizado]

Grabaciones del evento:

- AMD-Xilinx Platforms and Tools

- Introduction to High-Level Synthesis (44:31) https://www.youtube.com/watch?v=tz-LxplVp_g

- Vitis HLS Tool Flow y Demo 1 – Intro HLS (34:39) https://www.youtube.com/watch?v=OMkXfCfOdPg

- Kahoot 1 – podio

- Design Exploration with Directives (24:37) https://www.youtube.com/watch?v=ODbKHsSTpnc

- Introduction to IO Interfaces (21:39) https://www.youtube.com/watch?v=Mnf97mBzvv4

- Demo 2 – Directives & interfaces (25:45) https://www.youtube.com/watch?v=xoYGkuL5TvM

- Kahoot 2 – podio

- Introduction to the Vitis Unified Software Platform

- What’s New in Vitis HLS 2022.2

Profesores a cargo:

-

Sergio Lopez-Buedo

El Dr. Sergio López Buedo, es profesor contratado doctor en el área de Arquitectura y Tecnología de Computadores de la UAM y socio fundador de NAUDIT, una empresa de base tecnológica spin-off de dicha universidad. Tiene más de 15 años...Leer Más -

Gustavo Sutter

Doctor en informática y telecomunicaciones por la Universidad Autónoma de Madrid, Ingeniero en Sistemas en la Univ. Nacional del Centro de la Prov. de Buenos Aires en Argentina. Cuenta con más de 15 años de experiencia en diseño de sistemas...Leer Más -

Raúl Mateos Gil

Raúl Mateos Gil es doctor por la Universidad de Alcalá e Ingeniero de Telecomunicación por la Universidad Politécnica de Madrid. Actualmente es profesor titular del Departamento de Electrónica de la Universidad de Alcalá. Sus áreas de investigación se centran en...Leer Más