28-11-2023

Seminario: Los motores de IA (AI Engines) en AMD Versal Adaptive SoC

Seminar: The AI Engines in Versal Adaptive SoC

Este taller se relaciona con el seminario gratuito del 14 de septiembre de 2023 “Versal Adaptive SoC, la plataforma AMD-Xilinx de próxima generación” http://www.electratraining.org/2023/versal-adaptive-soc/

Presentación (In English below):

Este seminario se centra en los motores de IA en Versal, que pueden describirse como una matriz 2D de unidades de procesador VLIW SIMD RISC.

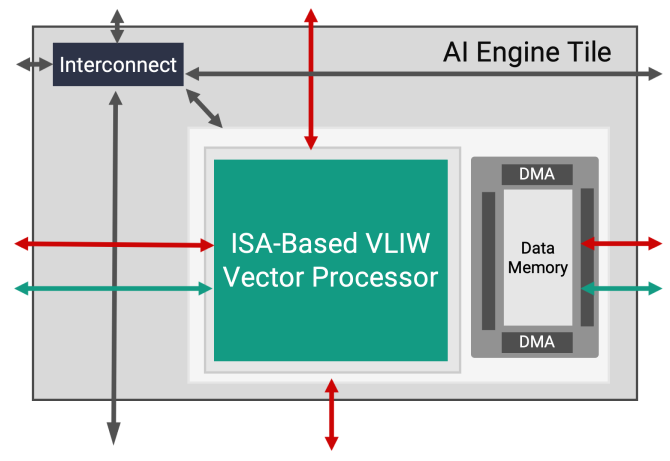

Los “tiles” (mosaicos / losetas / baldosas) de AI Engine (AIE) consisten en un procesador vectorial VLIW (Very Long Instruction Word), SIMD (Single Instruction Multiple Data) optimizado para aprendizaje automático y aplicaciones avanzadas de procesamiento de señales que logran un mayor rendimiento y funciones de baja latencia.

Describiremos la arquitectura de los AIE, el acceso a instrucciones únicas y múltiples, y los conceptos de paralelismo de los mosaicos AIE que permiten la descarga muy rápida y eficiente de funciones de software, típicamente desde los motores escalares (procesadores ARM) a estos motores cuando se necesita aceleración.

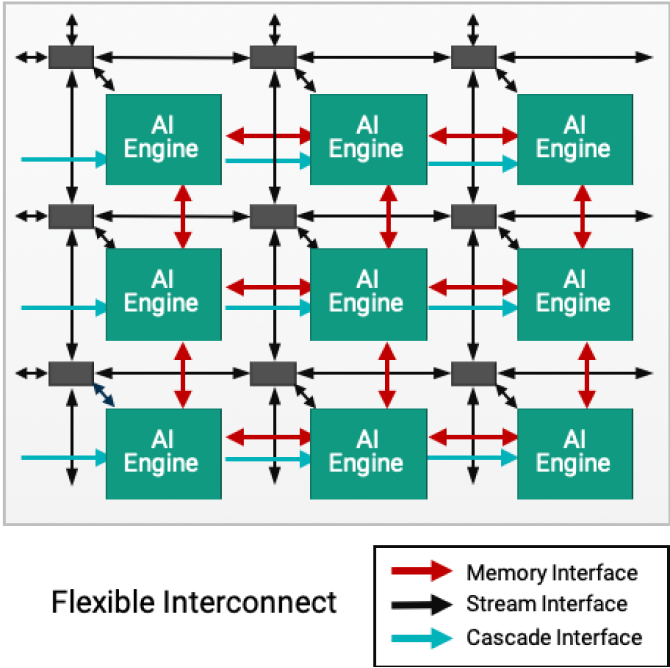

Se explicará la arquitectura de la interfaz que admite memorias privadas de memoria, compartir accesos a la memoria y transmisión de datos para admitir múltiples niveles de paralelismo.

AI Engine está programado con la toolchain (cadena de herramientas) de Vitis para ejecutar funciones de aceleración escritas en código C/C++. El manejo de las herramientas, incluidas las capacidades de depuración y las funciones de análisis, se presentan durante el seminario.

Introduction

This session will focus on the AI Engines in Versal which can be described as a 2D array of VLIW SIMD RISC processor units.

The AI Engine (AIE) tiles consist of a VLIW (Very Long Instruction Word), SIMD, (Single Instruction Multiple Data) vector processor optimized for machine learning and advanced signal processing applications achieving higher throughputs and low latency functions.

We describe the AIE architecture, single instruction and multiple instruction access, and parallelism concepts of the AIE tiles which allow highly fast and efficient offloading of software functions typically from the Scalar Engines (ARM processors) to these engines when acceleration is needed.

The interface architecture will be explained which supports memory private memories, sharing memory accesses, and data streaming to support multiple levels of parallelism.

The AI Engine is programmed with the Vitis toolchain to run acceleration functions written in C/C++ code. The handling of the tools, including debugging capabilities and analysis features, are introduced during the seminar.

*The seminar will be in Spanish.

This workshop is related to the free seminar on September 14, 2023 “Versal Adaptive SoC, the next generation AMD-Xilinx platform” http://www.electratraining.org/2023/versal-adaptive-soc/

Descriptores / Contents:

Información preliminar, más detalles en breve:

- Welcome and Introduction

- Introduction to the Versal AI Engine Architecture

- Vitis Tool Flow for Versal ACAP and AI Engine

- Application Partitioning on Versal ACAPs

- Data Types and Intrinsic Functions

- Data Movement and Vitis Analyzer

- The Programming Model: Single Kernel and Multiple Kernels Data Flow Graph

- Q&A

Fecha:

- Martes 28 de noviembre de 2023 de 14:00 a 18:00h. (horario coordinado Europeo de verano)

Date:

- Tuesday, november 28th 2023 14:00 – 18:00 CEST.

Lugar de realización / Place:

Live on Line

Pre-registro / Pre-registration:

Profesores a cargo:

-

Sergio Lopez-Buedo

El Dr. Sergio López Buedo, es profesor contratado doctor en el área de Arquitectura y Tecnología de Computadores de la UAM y socio fundador de NAUDIT, una empresa de base tecnológica spin-off de dicha universidad. Tiene más de 15 años...Leer Más -

Gustavo Sutter

Doctor en informática y telecomunicaciones por la Universidad Autónoma de Madrid, Ingeniero en Sistemas en la Univ. Nacional del Centro de la Prov. de Buenos Aires en Argentina. Cuenta con más de 15 años de experiencia en diseño de sistemas...Leer Más -

Raúl Mateos Gil

Raúl Mateos Gil es doctor por la Universidad de Alcalá e Ingeniero de Telecomunicación por la Universidad Politécnica de Madrid. Actualmente es profesor titular del Departamento de Electrónica de la Universidad de Alcalá. Sus áreas de investigación se centran en...Leer Más