Del 23-09-2024 al 25-09-2024

Síntesis de alto nivel (HLS) para FPGAs de AMD Xilinx con Vitis HLS

— Anuncio Preliminar

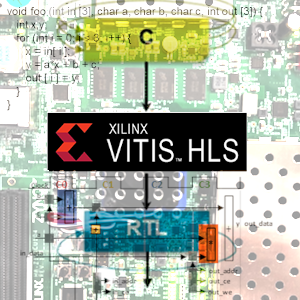

Síntesis de alto nivel para dispositivos AMD-Xilinx con Vitis-HLS

La necesidad de subir el nivel de abstracción para ganar productividad ha hecho de Síntesis del Alto Nivel (High Level Synthesis-HLS) una pieza clave para transformar descripciones algorítmicas en código RTL en tiempo inimaginables hace una década atrás. Vitis-HLS ha evolucionado convirtiéndose en una herramienta indispensable en el flujo de diseño basados en IP-cores utilizado en Vivado Design Suite. Así mismo, es parte esencial para la síntesis de hardware dentro de del entorno de desarrollo software Vitis (Vitis – Unified Software Platform).

Desde la versión 2020.2 de la herramienta Vivado-HLS se ha renombrado la herramienta como Vitis-HLS introduciendo múltiples cambios que favorecen la integración en el flujo de diseño

HLS01: High Level Synthesis for Xilinx FPGAs with Vitis-HLS

HLS01: Síntesis de alto nivel para FPGAs de Xilinx con Vitis-HLS

Breve Resumen: Completa Introducción a la herramienta de síntesis de alto nivel Vitis-HLS. Este curso cubre estrategias de síntesis, características de la herramienta, mejora de rendimiento, optimización en área, creación de interfaces, reducción de latencia, codificación de bancos de prueba (testbench), trucos y consejos de codificación. El temario ha sido actualizado para cubrir las novedades de la herramienta, así como la integración con Vitis (Unified Software Platform) y Vivado-HLS. Este curso es indispensable para el uso eficiente de VITIS tanto para aceleración, pero también para aumentar la productividad en diseños Hardware tradicionales. En esta nueva edición se agregan las consideraciones para migrar dese Vivado-HLS a Vitis-HLS y el soporte de nuevas directivas que aparecen. También se repasan conceptos de movimiento de datos entre PS-PL usando AXI-Slave y AXI-Master. El curso utiliza como plataforma de referencia Zynq UltraScale+ (MPSoC), aunque los conceptos son aplicables a toda la gama de dispositivos de AMD-Xilinx.

Descriptores y detalles:

- Puede consultar los detalles de la pasada edición 2023 (aquí). En breve descriptores 2024.

Fechas: laasada

- Lunes 23, martes 24 y miércoles 25 de septiembre 2024 de 9:00 a 18:00 hs

Lugar de realización:

Escuela Politécnica Superior

Universidad Autónoma de Madrid (UAM)

Francisco Tomás y Valiente, 11

28049 MADRID

Puede ver como llegar (Aquí).

Fundación Fundae:

Recuerde que su empresa puede beneficiarse de las subvenciones de la fundación fundae (antigua fundación tripartita)