Del 27-09-2021 al 30-09-2021

Taller práctico: Xilinx Versal ACAP y AI Engines

Workshop hands-on: Start working with Xilinx Versal ACAP and AI Engines

Taller práctico. Uso de Xilinx Versal ACAP y los motores AI

Podéis acceder a las grabaciones de algunas presentaciones del evento en este enlace

Información (flyer) en PDF aquí.

Presentación (In English below):

La aparición de esta nueva generación de plataformas de aceleración adaptable (ACAP – Adaptive Compute Acceleration Platforms) abre nuevas posibilidades para los desarrolladores de software y hardware.

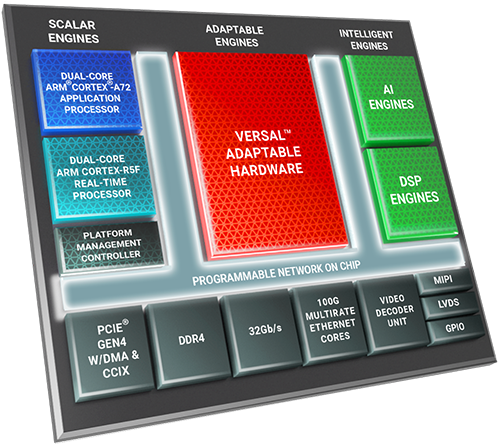

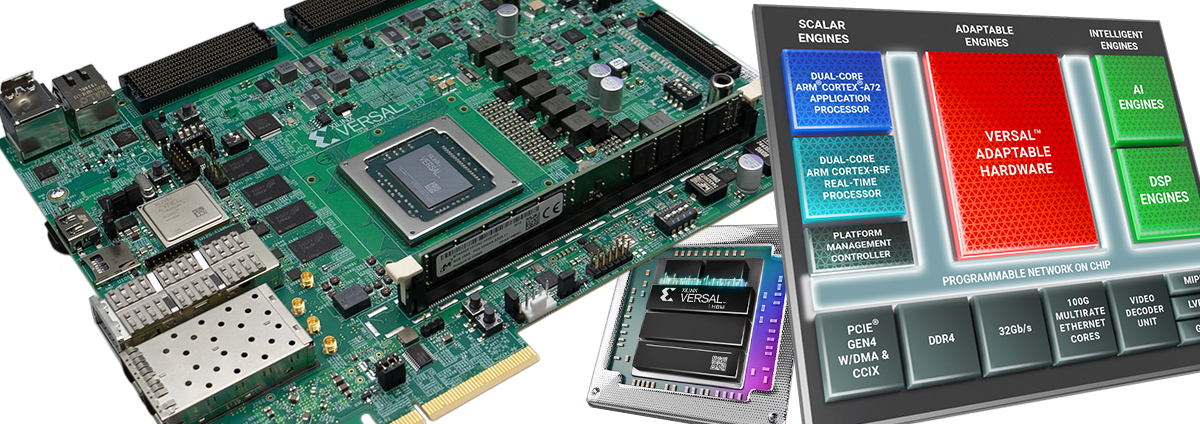

Estas plataformas integran una arquitectura de cómputo heterogénea con CPU, GPU y FPGA, lo que permite el desarrollo de motores escalares, adaptables e inteligentes, estrechamente acoplados con jerarquías de memoria personalizadas y una red en chip (NoC – Network on Chip). Esté a la vanguardia de las tecnologías FPGA y aprenda a utilizar la plataforma FPGA de próxima generación de Xilinx: ¡Versal® ACAP!

Esta formación práctica le proporcionará los conocimientos básicos para poner en marcha Versal ACAP para sus proyectos.

El curso patrocinado por Xilinx y ElectraTraining en su rol de training autorizado (ATP – Xilinx Authorized Training) permite comenzar a trabajar con la nueva plataforma Versal ACAP, explorar las características exclusivas de Versal, como los AI Engine y Network-on-Chip (NoC). Además obtendrá más información sobre los flujos de diseño en la herramienta de software unificado Vitis.

Se desarrolla en formato “blended”, una primera parte live on-line (2 días) y un día presencial. El curso se dicta en español. La primera parte de dos días Live-online tiene un coste de 99 dólares (85 €) gracias al soporte de Xilinx.

Introduction

The emergence of a new generation of Adaptive Compute Acceleration Platforms opens up new possibilities for both software and hardware developers.

These platforms integrate a heterogeneous compute architecture with CPUs, GPUs and FPGAs, enabling the development of scalar, adaptable and intelligent engines, tightly coupled with custom memory hierarchies and a Network-on-Chip.

Be at the forefront of FPGA technologies and learn how to use Xilinx next generation FPGA platform – Versal® ACAP! This hands-on training will equip you with the basic knowledge to kickstart Versal ACAP for your projects.

This course sponsored by Xilinx and its authorized trainings (ATP – Xilinx Authorized Training) allows you to start working with the new Versal ACAP platform, explore the exclusive features of Versal, such as the AI Engine and Network-on-Chip (NoC). You will also learn more about design flows in the Vitis Unified Software Tool.

It is organized in a “blended” format, a first part live-on-line of two days and a face-to-face day.

The first part of two days Live-online has a cost of 99 dollars thanks to the support of Xilinx. The course is taught in Spanish.

Precios:

- Parte 1: 2 días live-online (4 hs/día). Intro Xilinx Versal ACAP.

Valor original u$d 500 (425€), precio especial u$d 99 (85 €)* - Parte 2: 1 día presencial. More Versal, NoC+AIE

Valor original u$d 500 (425€), precio especial 50% descuento u$d 249 (212 €)

Promoción curso completo valor original u$d 1000 (10 TC), precio especial u$d 299 (255 €)

* Esta oferta es posible gracias al soporte de Xilinx

* Capacidad limitada (16 asistentes en presencial, 32 para el live-on-line)

* Disponemos de algunas medias becas disponibles

Special Rates:

- Part1: 2 days live-online (4 hs/day). Intro Versal ACAP.

Value u$d 500 (425€), special offer u$d 99 (85 €) - Part2: 1 day face-2-face. More Versal, NoC+AIE

Value u$d 500 (425€), special 50% off offer u$d 249 (212 €)

All together value u$d 1000 (10 TC), special offer. u$d 299 (255 €)

* This offer is possible due to Xilinx Support

* Limited seats (16 attendees in face to face, 32 in Live on Line)

* We have a few grants available

Descriptores / Contents:

Part1: Content 2 days live-online:

- Introduction. Talks about the need for Versal devices and gives an overview of the different Versal families.

- Architecture Overview. Provides a high-level overview of the Versal architecture, illustrating the various engines available in the Versal architecture.

- Design Tool Flow. Maps the various engines in the Versal architecture to the tools required and describes how to target them for final image assembly.

- Adaptable Engines (PL). Describes the logic resources available in the Adaptable Engine.

- Processing System. Reviews the Cortex™-A72 processor APU and Cortex-R5 processor RPU that form the Scalar Engine. The platform management controller (PMC), processing system manager (PSM), I/O peripherals, and PS-PL interfaces are also covered.

- PMC and Boot and Configuration. Describes the platform management controller, platform loader and manager (PLM) software and boot and configuration.

- SelectIO Resources. Describes the I/O bank, SelectIO™ interface, and I/O delay features.

- Clocking Architecture. Discusses the clocking architecture, clock buffers, clock routing, clock management functions, and clock de-skew.

- AI Engine, DSP58 and NoC Introduction. A first Introduction

Part2: Content 1 days face-2-face:

- Software Build Flow. Provides an overview of the different build flows, such as the do-it-yourself, Yocto Project, and PetaLinux tool flows.

- Software Stack. Reviews the Versal ACAP bare-metal, FreeRTOS, and Linux software stack and their components.

- System Interrupts. Discusses the different system interrupts and interrupt controllers.

- Timers, Counters, and RTC. Provides an overview of timers and counters, including the system counter, triple timer counter (TTC), watchdog timer, and real-time clock (RTC).

- DSP Engine. Describes the DSP58 slice and compares the DSP58 slice with the DSP48 slice. DSP58 modes are also covered in detail.

- AI Engine. Discusses the AI Engine array architecture, terminology, and AIE interfaces. Reviewing the data movement between AI Engines, between AI Engines via memory and DMA, and between AI Engines to programmable logic (PL)

- NoC Introduction and Concepts. Covers the reasons to use the network on chip, its basic

elements, and common terminology. - Device Memory. Describes the available memory resources, such as block RAM, UltraRAM, LUTRAM, embedded memory, OCM, and DDR. The integrated memory controllers are also covered.

- Programming Interfaces. Reviews the various programming interfaces in the Versal ACAP.

- Application Partitioning. Covers what application partitioning is and how the mapping of resources based on the models of computation can be performed.

Fechas:

- Parte1: lunes 27, martes 28 de septiembre de 2021 de 14:00 a 18:00h. (horario coordinado Europeo de verano)

- Parte2: jueves 30 de septiembre de 2021 de 10:00 a 18:00h.*

* Medidas COVID en cursos presenciales (Ver aquí).

Dates:

- Part1: Monday 27th, Tuesday 28th September 14:00 – 18:00 CEST.

- Part2: Thursday 30th September. 10:00 to 18:00 CEST

Lugar de realización:

Escuela Politécnica Superior

Universidad Autónoma de Madrid (UAM)

Francisco Tomás y Valiente, 11

28049 MADRID

Puede ver como llegar (Aquí).

Fundación Fundae:

Recuerde que su empresa puede beneficiarse de las subvenciones de la fundación fundae (antigua fundación tripartita)

Pre-registro:

[Evento Finalizado]

Profesores a cargo:

-

Sergio Lopez-Buedo

El Dr. Sergio López Buedo, es profesor contratado doctor en el área de Arquitectura y Tecnología de Computadores de la UAM y socio fundador de NAUDIT, una empresa de base tecnológica spin-off de dicha universidad. Tiene más de 15 años...Leer Más -

Gustavo Sutter

Doctor en informática y telecomunicaciones por la Universidad Autónoma de Madrid, Ingeniero en Sistemas en la Univ. Nacional del Centro de la Prov. de Buenos Aires en Argentina. Cuenta con más de 15 años de experiencia en diseño de sistemas...Leer Más -

Raúl Mateos Gil

Raúl Mateos Gil es doctor por la Universidad de Alcalá e Ingeniero de Telecomunicación por la Universidad Politécnica de Madrid. Actualmente es profesor titular del Departamento de Electrónica de la Universidad de Alcalá. Sus áreas de investigación se centran en...Leer Más